COMPUTER ORGANIZATION AND DESIGN

The Hardware/Software Interface

# **Chapter 1**

#### **Computer Abstractions and Technology**

# **The Computer Revolution**

- Progress in computer technology

- Underpinned by domain-specific accelerators

- Makes novel applications feasible

- Computers in automobiles

- Cell phones

- Human genome project

- World Wide Web

- Search Engines

- Computers are pervasive

## **Classes of Computers**

#### Personal computers

- General purpose, variety of software

- Subject to cost/performance tradeoff

- Server computers

- Network based

- High capacity, performance, reliability

- Range from small servers to building sized

# **Classes of Computers**

- Supercomputers

- Type of server

- High-end scientific and engineering calculations

- Highest capability but represent a small fraction of the overall computer market

#### Embedded computers

- Hidden as components of systems

- Stringent power/performance/cost constraints

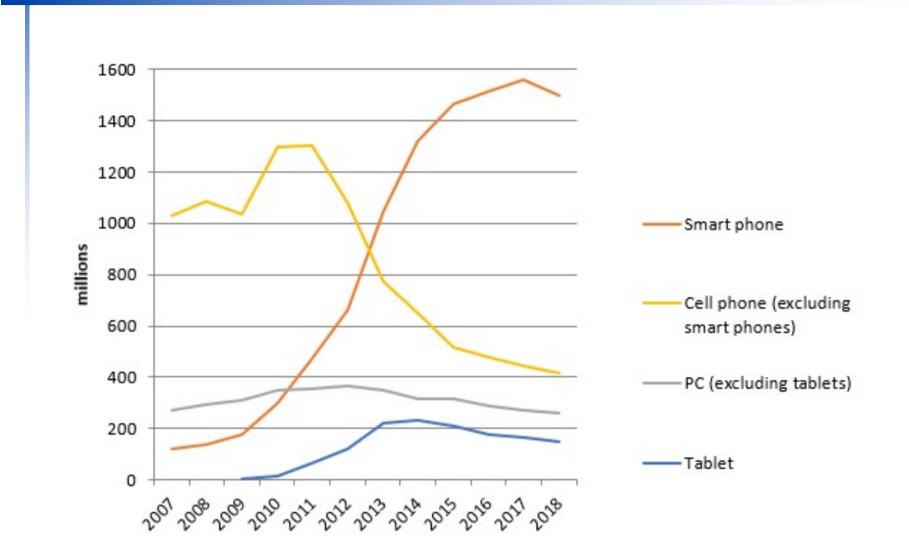

#### The PostPC Era

# The PostPC Era

- Personal Mobile Device (PMD)

- Battery operated

- Connects to the Internet

- Hundreds of dollars

- Smart phones, tablets, electronic glasses

- Cloud computing

- Warehouse Scale Computers (WSC)

- Software as a Service (SaaS)

- Portion of software run on a PMD and a portion run in the Cloud

- Amazon and Google

# What You Will Learn

- How programs are translated into the machine language

- And how the hardware executes them

- The hardware/software interface

- What determines program performance

- And how it can be improved

- How hardware designers improve performance

- What is parallel processing

# **Understanding Performance**

- Algorithm

- Determines number of operations executed

- Programming language, compiler, architecture

- Determine number of machine instructions executed per operation

- Processor and memory system

- Determine how fast instructions are executed

- I/O system (including OS)

- Determines how fast I/O operations are executed

### **Seven Great Ideas**

- Use *abstraction* to simplify design

- Make the common case fast

- Performance via parallelism

- Performance via pipelining

- Performance via prediction

- Hierarchy of memories

- Dependability via redundancy

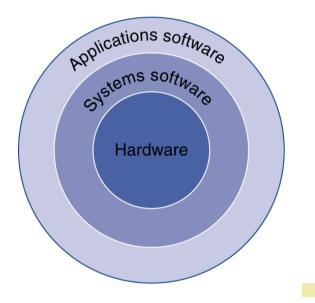

# **Below Your Program**

- Application software

- Written in high-level language

- System software

- Compiler: translates HLL code to machine code

- Operating System: service code

- Handling input/output

- Managing memory and storage

- Scheduling tasks & sharing resources

- Hardware

- Processor, memory, I/O controllers

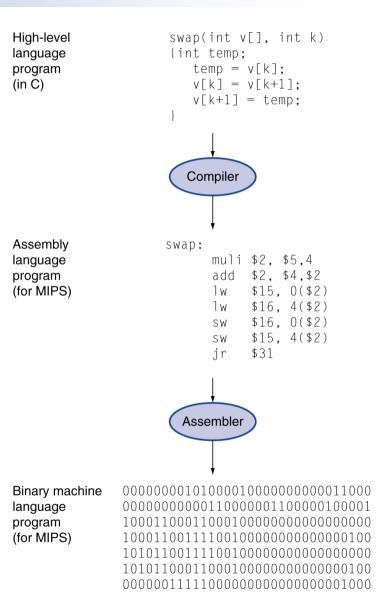

# Levels of Program Code

- High-level language

- Level of abstraction closer to problem domain

- Provides for productivity and portability

- Assembly language

- Textual representation of instructions

- Hardware representation

- Binary digits (bits)

- Encoded instructions and data

# **Components of a Computer**

- Same components for all kinds of computer

- Desktop, server, embedded

#### Input/output includes

- User-interface devices

- Display, keyboard, mouse

- Storage devices

- Hard disk, CD/DVD, flash

- Network adapters

- For communicating with other computers

### Touchscreen

- PostPC device

- Supersedes keyboard and mouse

- Resistive and Capacitive types

- Most tablets, smart phones use capacitive

- Capacitive allows multiple touches simultaneously

#### **Through the Looking Glass** LCD screen: picture elements (pixels) Mirrors content of frame buffer memory Frame buffer Raster scan CRT display $Y_0$ $Y_0$ Y<sub>1</sub> Y₁

$X_0 \quad X_1$

$X_0 \quad X_1$

### **Opening the Box**

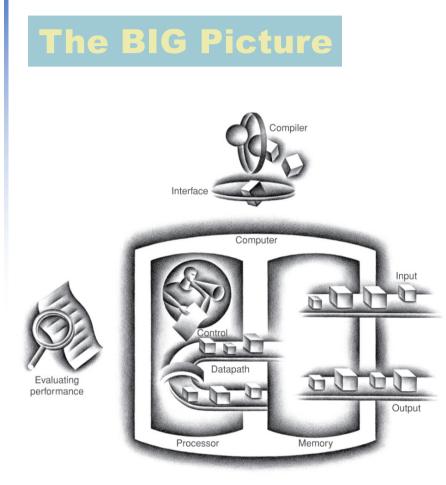

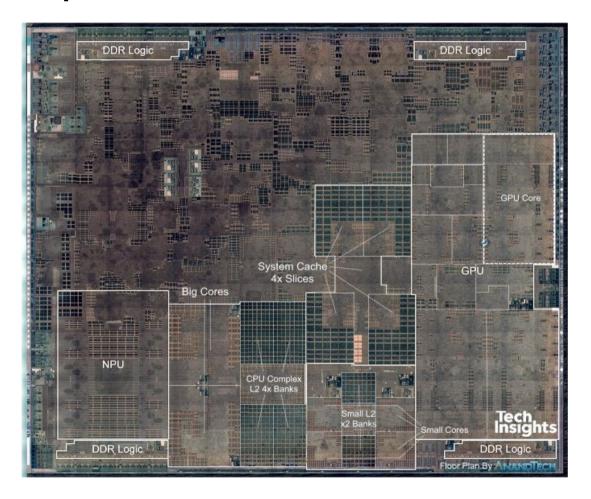

# Inside the Processor (CPU)

- Datapath: performs operations on data

- Control: sequences datapath, memory, …

- Cache memory

- Small fast SRAM memory for immediate access to data

#### **Inside the Processor**

#### A12 processor

### Abstractions

#### **The BIG Picture**

- Abstraction helps us deal with complexity

Hide lower-level detail

- Instruction set architecture (ISA)

- The hardware/software interface

- Application binary interface

- The ISA plus system software interface

- Implementation

- The details underlying and interface

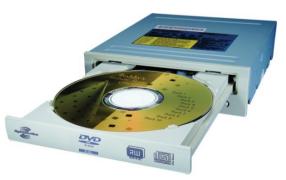

## A Safe Place for Data

- Volatile main memory

- Loses instructions and data when power off

- Non-volatile secondary memory

- Magnetic disk

- Flash memory

- Optical disk (CDROM, DVD)

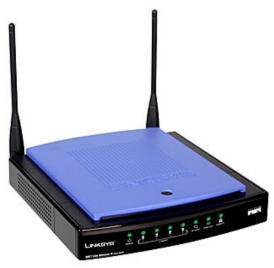

## Networks

- Communication, resource sharing, nonlocal access

- Local area network (LAN): Ethernet

- Wide area network (WAN): the Internet

- Wireless network: WiFi, Bluetooth

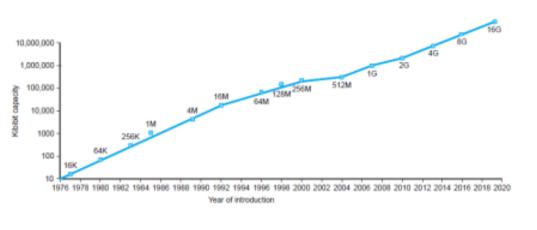

# **Technology Trends**

- Electronics technology continues to evolve

- Increased capacity and performance

- Reduced cost

DRAM capacity

| Year | Technology                 | Relative performance/cost |

|------|----------------------------|---------------------------|

| 1951 | Vacuum tube                | 1                         |

| 1965 | Transistor                 | 35                        |

| 1975 | Integrated circuit (IC)    | 900                       |

| 1995 | Very large scale IC (VLSI) | 2,400,000                 |

| 2013 | Ultra large scale IC       | 250,000,000,000           |

# **Semiconductor Technology**

- Silicon: semiconductor

- Add materials to transform properties:

- Conductors

- Insulators

- Switch

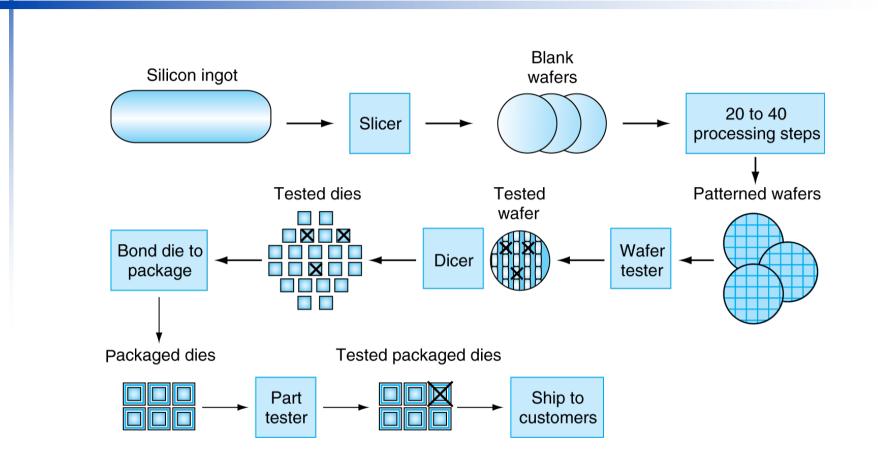

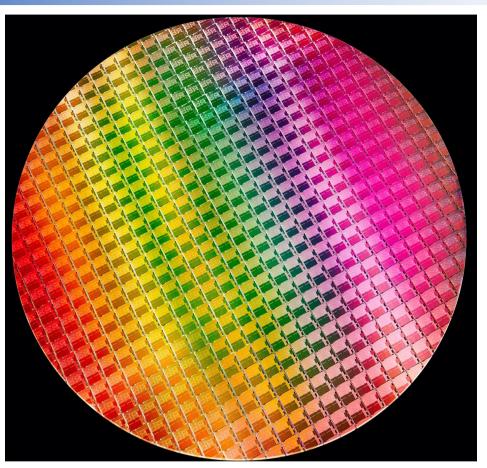

# **Manufacturing ICs**

#### Yield: proportion of working dies per wafer

#### Intel® Core 10<sup>th</sup> Gen

300mm wafer, 506 chips, 10nm technology

Each chip is 11.4 x 10.7 mm

# **Integrated Circuit Cost**

Cost per die =

$$\frac{\text{Cost per wafer}}{\text{Dies per wafer } \times \text{Yield}}$$

Dies per wafer  $\approx$  Wafer area/Die area

Yield =  $\frac{1}{(1+(\text{Defects per area} \times \text{Die area}/2))^2}$

#### Nonlinear relation to area and defect rate

- Wafer cost and area are fixed

- Defect rate determined by manufacturing process

- Die area determined by architecture and circuit design